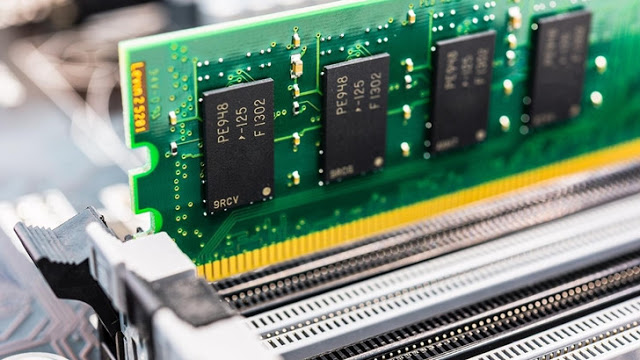

A diffarenza trà DDR4 è DDR5 RAM hè in velocità è capacità

Sicondu JEDEC, a prossima generazione di memoria d'accessu aleatoriu DDR5 (RAM) serà duie volte più veloce di a RAM DDR4 attuale quandu hè stata liberata.

JEDEC hà annunziatu chì finalizà i normi DDR5 in qualchì tempu in 2018, è l'urganizazione dice chì DDR5 duppià a larghezza di banda è a densità nantu à DDR4, è vene cun un aumentu di l'efficienza energetica.

Ancu se u standard diventerà ufficiale l'annu prossimu, a nova generazione ùn serà pronta per i fabricatori finu à dopu à 2020.

Hè da nutà chì u standard DDR4 hè statu finalizatu in 2012, ma ùn era micca finu à 2015, quandu i prucessori è i SoC anu da esse aghjurnati per sustene.

Cosa hè DDR5

GDDR5 (Dual Graphics Data Rate v5) SDRAM hè un tipu di carta grafica DRAM d'altu rendiment cuncepitu per l'applicazioni di l'informatica di larghezza di banda alta.

Cum'è u so predecessore, GDDR4, hè basatu annantu à GDDR5 SDRAM DDR3 chì hà duie volte e linee di dati cà DDR2 SDRAM, ma cuntene ancu GDDR5 di 8-bit wide prefetch buffer simili à GDDR4. GDDR5 SGRAM hè conforme à i normi citati in a specificazione GDDR5 da JEDEC. Utiliza l'interfaccia di l'architettura di prefetch DDR 8N per un rendimentu elevatu è u funziunamentu chì pò esse cunfiguratu per eseguisce in modalità 32 x o 16 x (clamshell) rilevata durante l'inizializazione di u dispositivu. L'interfaccia di trasportu GDDR5 2 hà una parolla di clock 32-bit per ciclu (WCK) scrive di dati à / da i pin I / O. L'accessu currispundente hè custituitu da u prefetch -8N,

O scrivite o leghje, da u ciculu di trasferimentu di dati CK 2 nantu à un clock largu 256-bit. U core di a memoria interna cuntene ottu trasferimenti di dati WCK nantu à un semiciclu chì currisponde à a larghezza di 32-bit à i pin I / O.

A diffarenza trà DDR4 è DDR5

GDDR5 funziona cù diversi tipi di clock. U cumandamentu di diffarenza di clock (CK) cum'è riferimentu per l'indirizzu è l'input di cumanda, scrivite a diffarenza di clock (WCK) cum'è riferimentu chì leghje è scrive. Per esse più precisu, u mira di SGRAM GDDR5 clocks, ognunu di elli stabilitu à dui bytes.

U WCK opera à a frequenza duie volte di CK. Pigliendu GDDR5 cù 5 Gbit / s data rate per pin per esempiu, u clock CK travaglia cù 1.25 GHz è WCK cù 2.5 GHz.

L'orologi CK è WCK seranu allinati durante l'inizializazione è a furmazione di a sequenza. Questa cumpatibilità permette a lettura è a scrittura cù una latenza minima. Single GDDR32 5-bit è Pin Pins, e nostre applicazioni anu dimustratu è campionatu GDDR5, è dimustratu un documentu nantu à e tecnulugia daretu à GDDR5.

. U 10 di maghju di u 2008, Kimunda annuncia volumi di produzzione di 512 moduli GDDR5 valutati à 3.6 Gbit/s (900 MHz), 4.0 Gbit/s (1 GHz) è 4.5 Gbit/s (1.125 GHz). Per più infurmazione, visitate Wikipedia