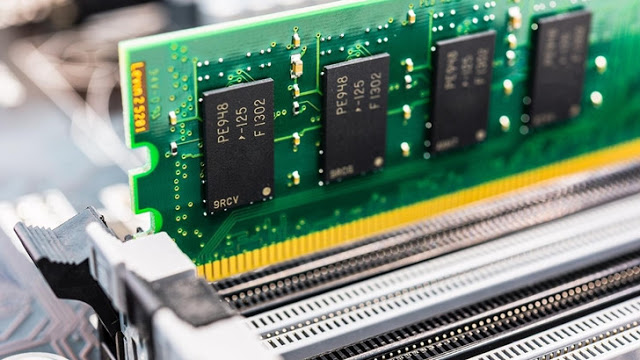

Forskellen mellem DDR4 og DDR5 RAM er i hastighed og muligheder

Ifølge JEDEC vil den næste generations DDR5 -hukommelse med tilfældig adgang (RAM) være dobbelt så hurtig som den nuværende DDR4 -RAM, da den blev frigivet.

JEDEC har annonceret, at de vil færdiggøre DDR5-standarderne engang i 2018, og organisationen siger, at DDR5 vil fordoble båndbredden og tætheden i forhold til DDR4 og komme med en stigning i strømeffektiviteten.

Selvom standarden bliver officiel næste år, vil den nye generation først være klar til producenter efter 2020.

Det er værd at bemærke, at DDR4 -standarden blev færdiggjort i 2012, men det var først i 2015, da processorer og SoC'er skulle opdateres for at understøtte den.

Hvad er DDR5

GDDR5 (Dual Graphics Data Rate Version 5) SDRAM er en type højtydende DRAM-grafikkort designet til computerapplikationer med høj båndbredde.

Ligesom sin forgænger, GDDR4, er den baseret på GDDR5 SDRAM DDR3, som har dobbelt så mange datalinjer end DDR2 SDRAM, men den indeholder også GDDR5 med 8-bit brede forhåndshentningsbuffere svarende til GDDR4. GDDR5 SGRAM overholder de standarder, der er nævnt i GDDR5 -specifikationen af JEDEC. Den bruger DDR 8N-prefetch-arkitekturgrænsefladen til at opnå høj ydeevne og drift, der kan konfigureres til at køre i 32 x eller 16 x (clamshell)-tilstand registreret under initialisering af enheden. GDDR5 2 transportgrænseflade har en 32-bit clock word per cycle (WCK) skrivning af data til/fra I/O benene. Den tilsvarende adgang består af -8N prefetch,

Eller skriv eller læs fra CK 2 dataoverførselscyklussen på et 256-bit bredt ur. Den interne hukommelseskerne indeholder otte WCK-dataoverførsler på en halv cyklus svarende til 32-bit bredde ved I/O-benene.

Forskellen mellem DDR4 og DDR5

GDDR5 fungerer med forskellige urtyper. Clock difference-kommandoen (CK) som reference for adresse- og kommandoinput, skriv clock difference (WCK) som en reference, der læser og skriver. For at være mere præcis, målet for SGRAM GDDR5 ure, hver af dem sat til to bytes.

WCK'en opererer med to gange CK's frekvens. Når man tager GDDR5 med 5 Gbit/s datahastighed pr. Pin som et eksempel, fungerer CK -uret med 1.25 GHz og WCK med 2.5 GHz.

CK- og WCK-ure vil blive justeret under initialisering og træning af sekvensen. Denne kompatibilitet muliggør læsning og skrivning med minimal forsinkelse. Enkelt 32-bit GDDR5 og Pin Pins, vores applikationer har demonstreret og prøvetaget GDDR5 og demonstreret et papir om teknologierne bag GDDR5

. Den 10. maj 2008 annoncerede Kimunda produktionsmængder på 512 GDDR5 -moduler vurderet til 3.6 Gbit/s (900 MHz), 4.0 Gbit/s (1 GHz) og 4.5 Gbit/s (1.125 GHz). For mere information, besøg Wikipedia