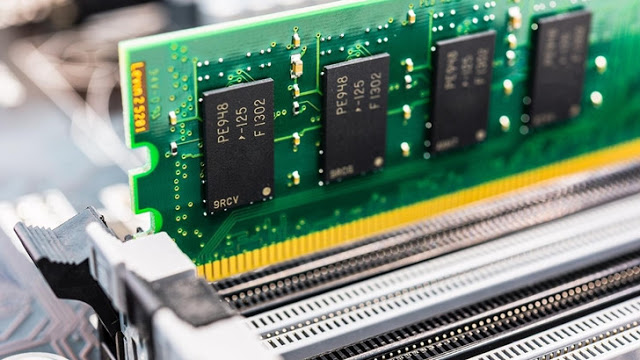

DDR4 eta DDR5 RAM arteko aldea abiaduran eta gaitasunetan dago

JEDECen arabera, hurrengo belaunaldiko DDR5 ausazko sarbide memoria (RAM) egungo DDR4 RAM baino bi aldiz azkarragoa izango da kaleratu zenean.

JEDECek iragarri du 5an DDR2018 estandarrak amaituko dituela, eta erakundeak dio DDR5ek banda zabalera eta dentsitatea bikoiztu egingo dituela DDR4ren gainean, eta potentzia-eraginkortasuna handituko duela.

Datorren urtean estandarra ofiziala izango den arren, belaunaldi berria ez da fabrikatzaileentzat prest egongo 2020a igaro arte.

Aipatzekoa da DDR4 estandarra 2012an amaitu zela, baina 2015era arte ez zen izan, prozesadoreak eta SoC-ak eguneratu behar izan baitzituzten onartzeko.

Zer da DDR5

GDDR5 (Dual Graphics Data Rate Version 5) SDRAM banda-zabalera handiko aplikazio informatikoetarako diseinatutako errendimendu handiko DRAM txartel grafiko mota bat da.

Bere aurrekoa den GDDR4 bezala, GDDR5 SDRAM DDR3-n oinarritzen da, DDR2 SDRAM baino datu-lerro bikoitza dituena, baina GDDR5-ren antzeko 8 biteko aurre-bilketa-buffer zabaleko GDDR4 ere badu. GDDR5 SGRAM-ek JEDECek GDDR5 zehaztapenean aipatutako estandarrak betetzen ditu. DDR 8N prefetch arkitektura interfazea erabiltzen du errendimendu eta funtzionamendu altua lortzeko, 32 x edo 16 x (clamshell) moduan exekutatzeko konfiguratu daitekeena gailua hastean detektatuta. GDDR5 2 garraio interfazeak 32 biteko erloju-hitza du ziklo bakoitzeko (WCK) datuen idazketa I/O pinetan. Dagokion sarbidea -8N aurreskua da,

Edo idatzi edo irakurri, CK 2 datu-transferentzia ziklotik 256 biteko zabaleko erloju batean. Barne memoria-nukleoak zortzi WCK datu-transferentzia ditu ziklo erdian, 32 biteko zabalerari dagokion I/O pinetan.

DDR4 eta DDR5 arteko aldea

GDDR5 erloju mota ezberdinekin funtzionatzen du. Erlojuaren diferentzia komandoa (CK) helbidea eta komandoen sarreretarako erreferentzia gisa, idatzi erlojuaren diferentzia (WCK) irakurtzen eta idazten duen erreferentzia gisa. Zehatzago esateko, SGRAM GDDR5 erlojuen xedea, horietako bakoitza bi byteko ezarrita.

WCK-k CKren maiztasun bikoitzan funtzionatzen du. Pin bakoitzeko 5 Gbit/s datu-tasa duen GDDR5 hartuta, adibide gisa, CK erlojuak 1.25 GHz-ekin funtzionatzen du eta WCK 2.5 GHz-ekin.

CK eta WCK erlojuak lerrokatuko dira sekuentziaren hasieraketan eta entrenatzean. Bateragarritasun honek latentzia minimoarekin irakurtzea eta idaztea ahalbidetzen du. 32 biteko GDDR5 eta Pin Pin bakarrak, gure aplikazioek GDDR5 frogatu eta lagintu dute, eta GDDR5 atzean dauden teknologiei buruzko dokumentu bat erakutsi dute.

. 10ko maiatzaren 2008ean, Kimundak 512 Gbit/s (5 MHz), 3.6 Gbit/s (900 GHz) eta 4.0 Gbit/s (1 GHz) 4.5 GDDR1.125 moduluen ekoizpen-bolumenak iragarri zituen. Informazio gehiagorako, bisitatu Wikipedia