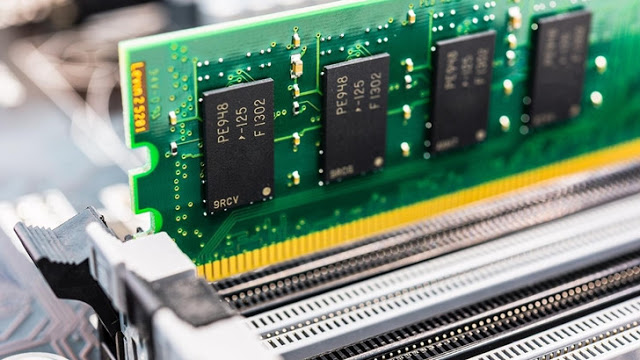

ʻO ka ʻokoʻa ma waena o DDR4 a me DDR5 RAM i ka wikiwiki a me nā hiki

Wahi a ka hui e pili ana i nā kūlana hoʻomanaʻo kamepiula i kapa ʻia ʻo "JEDEC", ʻo ka hanauna hou o DDR5 random access memory ("RAM") e ʻelua ʻoi aku ka wikiwiki o ka DDR4 RAM o kēia manawa i ka wā i hoʻokuʻu ʻia ai.

Ua hoʻolaha ʻo JEDEC e hoʻopau i nā kūlana DDR5 i kekahi manawa ma 2018, a ʻōlelo ka hui e pāpālua ʻo DDR5 i ka bandwidth a me ka density ma luna o DDR4, a e hele mai me ka hoʻonui ʻana i ka pono o ka mana.

ʻOiai e lilo ka maʻamau i ka makahiki aʻe, ʻaʻole mākaukau ka hanauna hou no nā mea hana a hiki i ka 2020.

Pono e hoʻomaopopo ʻia ua hoʻopau ʻia ka maʻamau DDR4 ma 2012, akā ʻaʻole ia a hiki i 2015, i ka manawa e hoʻonui ʻia ai nā kaʻina hana a me nā SoC e kākoʻo iā ia.

He aha ka DDR5

ʻO GDDR5 (Dual Graphics Data Rate Version 5) ʻO SDRAM kahi ʻano kāleka kiʻi DRAM kiʻekiʻe i hoʻolālā ʻia no nā polokalamu kamepiula bandwidth kiʻekiʻe.

E like me kona mea ma mua, GDDR4, ua hoʻokumu ʻia ia ma GDDR5 SDRAM DDR3 i ʻelua mau laina ʻikepili e like me DDR2 SDRAM, akā aia pū kekahi GDDR5 mai 8-bit wide prefetch buffers like me GDDR4. Hoʻopili ʻo GDDR5 SGRAM i nā kūlana i ʻōlelo ʻia ma ka kikoʻī GDDR5 e JEDEC. Hoʻohana ia i ka DDR 8N prefetch architecture interface no ka hana kiʻekiʻe a me ka hana i hiki ke hoʻonohonoho ʻia e holo ma 32 x a i ʻole 16 x (clamshell) mode i ʻike ʻia i ka wā o ka hoʻomaka ʻana o ka hāmeʻa. Loaʻa iā GDDR5 2 kahi huaʻōlelo uaki 32-bit no kēlā me kēia pōʻaiapili (WCK) kākau ʻikepili i/mai nā pine I/O. Loaʻa ka loaʻa ʻana o ka -8N prefetch,

A i ʻole e kākau a heluhelu paha, mai ka pōʻai hoʻoili ʻikepili CK 2 ma kahi uaki ākea 256-bit. Aia i loko o ka waihona hoʻomanaʻo hoʻomanaʻo he ʻewalu mau hoʻoili ʻikepili WCK ma ka uaki hapalua like me ka laula o 32 bits ma nā pine I/O.

ʻO ka ʻokoʻa ma waena o DDR4 a me DDR5

Hana ʻo GDDR5 me nā ʻano uaki like ʻole. ʻO ke kauoha ʻokoʻa uaki (CK) ma ke ʻano he kuhikuhi no ka helu wahi a me nā hoʻokomo kauoha, e kākau i ka ʻokoʻa uaki (WCK) ma ke ʻano he kuhikuhi e heluhelu a kākau. E ʻoi aku ka pololei, ʻo ka pahuhopu o nā uaki SGRAM GDDR5, hoʻonohonoho kēlā me kēia i ʻelua bytes.

Hoʻohana ʻia ka WCK i ʻelua alapine o CK. Ke lawe nei i ka GDDR5 me 5 Gbit/s ka helu ʻikepili i kēlā me kēia pine ma ke ʻano he laʻana, hana ka uaki CK me 1.25 GHz a me WCK me 2.5 GHz.

E hoʻopili ʻia nā uaki CK a me WCK i ka wā o ka hoʻomaka ʻana a me ke aʻo ʻana o ke kaʻina. Hiki i kēia hoʻohālikelike ke heluhelu a me ke kākau ʻana me ka liʻiliʻi liʻiliʻi. Hoʻokahi 32-bit GDDR5 a me Pin Pins, ua hōʻike a hōʻike kā mākou mau noi iā GDDR5, a hōʻike i kahi pepa e pili ana i nā ʻenehana ma hope o GDDR5

. Ma Mei 10, 2008, ua hoʻolaha ʻo Kimunda i nā puke hana o 512 GDDR5 modules i helu ʻia ma 3.6 Gbit/s (900 MHz), 4.0 Gbit/s (1 GHz), a me 4.5 Gbit/s (1.125 GHz). No ka 'ike hou aku, e kipa Wikipedia