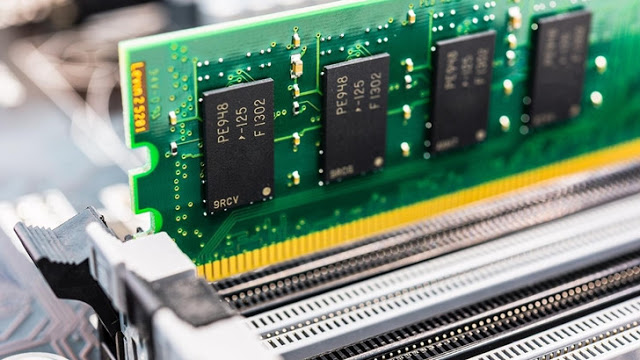

Id-differenza bejn DDR4 u DDR5 RAM hija fil-veloċità u l-kapaċitajiet

Skont l-organizzazzjoni responsabbli għall-istandards tal-memorja tal-kompjuter magħrufa bħala "JEDEC", il-ġenerazzjoni li jmiss ta 'memorja ta' aċċess każwali DDR5 ("RAM") se tkun id-doppju ta 'l-RAM DDR4 attwali meta ġiet rilaxxata.

JEDEC ħabbar li se jiffinalizza l-istandards DDR5 f'xi żmien fl-2018, u l-organizzazzjoni tgħid li DDR5 se jirdoppja l-bandwidth u d-densità fuq DDR4, u jiġi b'żieda fl-effiċjenza tal-enerġija.

Għalkemm l-istandard se jsir uffiċjali s-sena d-dieħla, il-ġenerazzjoni l-ġdida mhux se tkun lesta għall-manifatturi qabel l-2020.

Ta 'min jinnota li l-istandard DDR4 ġie ffinalizzat fl-2012, iżda ma kienx qabel l-2015, meta l-proċessuri u s-SoCs kellhom jiġu aġġornati biex isostnuh.

X'inhu DDR5

GDDR5 (Dual Graphics Data Rate Version 5) SDRAM huwa tip ta 'karta grafika DRAM ta' prestazzjoni għolja ddisinjata għal applikazzjonijiet tal-kompjuter b'wisa' ta 'frekwenza għolja.

Bħall-predeċessur tiegħu, GDDR4, huwa bbażat fuq GDDR5 SDRAM DDR3 li għandu d-doppju tal-linji tad-dejta bħal DDR2 SDRAM, iżda fih ukoll GDDR5 ta 'buffers ta' prefetch wiesgħa 8-bit simili għal GDDR4. GDDR5 SGRAM jikkonforma mal-istandards imsemmija fl-ispeċifikazzjoni GDDR5 minn JEDEC. Juża interface ta 'arkitettura DDR 8N prefetch għal prestazzjoni għolja u tħaddim li jistgħu jiġu kkonfigurati biex jaħdmu fil-modalità 32 x jew 16 x (clamshell) misjuba waqt l-inizjalizzazzjoni tal-apparat. L-interface tat-trasport GDDR5 2 għandha kelma ta 'arloġġ ta' 32 bit għal kull ċiklu (WCK) ta 'kitba ta' dejta lejn/mill-pinnijiet I/O. L-aċċess korrispondenti jikkonsisti mill-prefetch -8N,

Jew ikteb jew aqra, miċ-ċiklu tat-trasferiment tad-dejta CK 2 fuq arloġġ wiesa '256-bit. Il-qalba tal-memorja interna fiha tmien trasferimenti tad-dejta WCK fuq arloġġ ta 'nofs ċiklu korrispondenti b'wisa' ta '32 bit fil-pins I/O.

Id-differenza bejn DDR4 u DDR5

GDDR5 jaħdem b'tip ta 'arloġġ differenti. Il-kmand tad-differenza tal-arloġġ (CK) bħala referenza għall-inputs tal-indirizz u l-kmand, ikteb id-differenza tal-arloġġ (WCK) bħala referenza li taqra u tikteb. Biex tkun aktar preċiża, il-mira ta 'arloġġi SGRAM GDDR5, kull wieħed minnhom stabbilit għal żewġ bytes.

Il-WCK jaħdem bi frekwenza darbtejn CK. Meta tieħu GDDR5 b'rata tad-dejta ta '5 Gbit/s għal kull pin bħala eżempju, l-arloġġ CK jaħdem b'1.25 GHz u WCK b'2.5 GHz.

L-arloġġi CK u WCK se jkunu allinjati waqt l-inizjalizzazzjoni u t-taħriġ tas-sekwenza. Din il-kompatibilità tippermetti l-qari u l-kitba b'latenza minima. GDDR32 u Pin Pins Uniċi ta' 5-bit, l-applikazzjonijiet tagħna wrew u kampjunaw GDDR5, u wrew dokument dwar it-teknoloġiji wara GDDR5

. Fl-10 ta' Mejju, 2008, Kimunda ħabbret volum ta' produzzjoni ta' 512-il modulu GDDR5 stmat għal 3.6 Gbit/s (900 MHz), 4.0 Gbit/s (1 GHz), u 4.5 Gbit/s (1.125 GHz). Għal aktar informazzjoni, żur Wikipedija