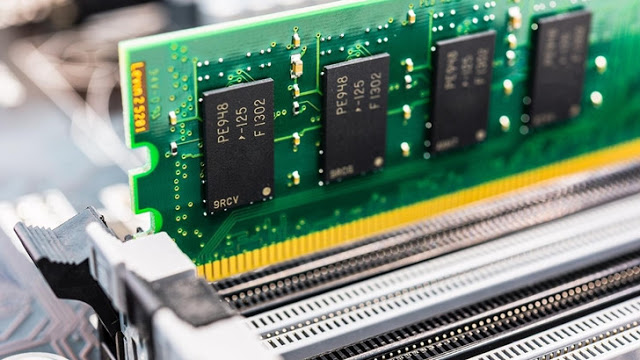

DDR4 နှင့် DDR5 RAM အကြား ခြားနားချက်မှာ မြန်နှုန်းနှင့် လုပ်ဆောင်နိုင်စွမ်းများဖြစ်သည်။

JEDEC ၏ အဆိုအရ လာမည့်မျိုးဆက် DDR5 random access memory (RAM) သည် လက်ရှိ DDR4 RAM ထက် နှစ်ဆပိုမိုမြန်ဆန်မည်ဖြစ်သည်။

JEDEC သည် 5 တွင် DDR2018 စံနှုန်းများကို အပြီးသတ်နိုင်လိမ့်မည်ဟု ကြေညာထားပြီး DDR5 သည် DDR4 ထက် bandwidth နှင့် သိပ်သည်းဆကို နှစ်ဆတိုးစေပြီး ပါဝါထိရောက်မှု တိုးလာသည်ဟု ဆိုသည်။

စံနှုန်းသည် လာမည့်နှစ်တွင် တရားဝင်ဖြစ်လာမည်ဖြစ်သော်လည်း မျိုးဆက်သစ်သည် 2020 နောက်ပိုင်းအထိ ထုတ်လုပ်သူများအတွက် အဆင်သင့်မဖြစ်သေးပါ။

DDR4 စံနှုန်းကို 2012 ခုနှစ်တွင် အပြီးသတ်ခဲ့ကြောင်း မှတ်သားရသော်လည်း ၎င်းကို ပံ့ပိုးရန်အတွက် ပရိုဆက်ဆာများနှင့် SoCs များကို အပ်ဒိတ်လုပ်ထားသည့်အခါ 2015 ခုနှစ်အထိ ဖြစ်မလာသေးပါ။

DDR5 ဆိုတာဘာလဲ

GDDR5 (Dual Graphics Data Rate ဗားရှင်း 5) SDRAM သည် bandwidth မြင့်မားသော ကွန်ပျူတာ အပလီကေးရှင်းများအတွက် ဒီဇိုင်းထုတ်ထားသော စွမ်းဆောင်ရည်မြင့် DRAM ဂရပ်ဖစ်ကတ် အမျိုးအစားတစ်ခုဖြစ်သည်။

၎င်း၏အရင် GDDR4 ကဲ့သို့ပင်၊ ၎င်းသည် DDR5 SDRAM ထက် ဒေတာလိုင်းနှစ်ဆရှိသော GDDR3 SDRAM DDR2 ကိုအခြေခံထားပြီး ၎င်းတွင် GDDR5 ၏ 8-bit wide prefetch buffers များပါရှိသည်။ GDDR4 SGRAM သည် JEDEC ၏ GDDR5 သတ်မှတ်ချက်တွင် ဖော်ပြထားသော စံနှုန်းများနှင့် ကိုက်ညီပါသည်။ ၎င်းသည် စက်ပစ္စည်းစတင်စဉ်အတွင်း တွေ့ရှိခဲ့သော 5 x သို့မဟုတ် 8 x (clamshell) မုဒ်တွင် လည်ပတ်ရန် မြင့်မားသောစွမ်းဆောင်ရည်နှင့် လည်ပတ်မှုကို ရရှိစေရန်အတွက် ၎င်းသည် DDR 32N prefetch ဗိသုကာအင်တာဖေ့စ်ကို အသုံးပြုသည်။ GDDR16 5 သယ်ယူပို့ဆောင်ရေးအင်တာဖေ့စ်တွင် I/O ပင်နံပါတ်များသို့ ဒေတာများရေးခြင်း 2-bit နာရီစကားလုံး (WCK) ပါရှိသည်။ သက်ဆိုင်သောဝင်ရောက်ခွင့်တွင် -32N prefetch ပါဝင်သည်၊

2-bit wide clock တွင် CK 256 data transfer cycle မှ စာရေးခြင်း သို့မဟုတ် ဖတ်ပါ။ အတွင်းမှတ်ဉာဏ် core တွင် I/O pins များရှိ 32-bit width နှင့် ကိုက်ညီသော လည်ပတ်မှုတစ်ဝက်တွင် WCK ဒေတာလွှဲပြောင်းမှု ရှစ်ခုပါရှိသည်။

DDR4 နှင့် DDR5 အကြားကွာခြားချက်

GDDR5 သည် မတူညီသော နာရီအမျိုးအစားနှင့် အလုပ်လုပ်သည်။ လိပ်စာနှင့် အမိန့်ပေးထည့်သွင်းမှုများအတွက် ရည်ညွှန်းချက်အဖြစ် နာရီခြားနားချက် (CK)၊ နာရီခြားနားချက် (WCK) ကို ဖတ်ရှုပြီး ရေးသားသည့် ကိုးကားချက်အဖြစ် ရေးပါ။ ပိုမိုတိကျစေရန်အတွက်၊ SGRAM GDDR5 နာရီများ၏ပစ်မှတ်ကို ၎င်းတို့တစ်ခုစီမှ နှစ်ဘိုက်အထိ သတ်မှတ်ထားသည်။

WCK သည် CK ၏ ကြိမ်နှုန်း နှစ်ကြိမ်ဖြင့် လုပ်ဆောင်သည်။ ဥပမာတစ်ခုအနေဖြင့် pin တစ်ခုလျှင် 5 Gbit/s ဒေတာနှုန်းဖြင့် GDDR5 ကိုယူ၍ CK နာရီသည် 1.25 GHz နှင့် WCK 2.5 GHz ဖြင့်အလုပ်လုပ်သည်။

CK နှင့် WCK နာရီများသည် စီးရီး၏ အစပြုခြင်းနှင့် လေ့ကျင့်မှုအတွင်း ချိန်ညှိမည်ဖြစ်သည်။ ဤသဟဇာတဖြစ်မှုသည် latency အနည်းဆုံးဖြင့် စာဖတ်ခြင်းနှင့် စာရေးခြင်းတို့ကို လုပ်ဆောင်နိုင်သည်။ တစ်ခုတည်းသော 32-bit GDDR5 နှင့် Pin Pins၊ ကျွန်ုပ်တို့၏ အပလီကေးရှင်းများက GDDR5 ကို နမူနာပြပြီး GDDR5 နောက်ကွယ်ရှိ နည်းပညာများကို စာရွက်ပေါ်တွင် သရုပ်ပြထားသည်။

. မေလ 10၊ 2008 တွင် Kimunda သည် 512 Gbit/s (5 MHz), 3.6 Gbit/s (900 GHz) နှင့် 4.0 Gbit/s (1 GHz) ဖြင့် အဆင့်သတ်မှတ်ထားသော 4.5 GDDR1.125 module များ၏ ထုတ်လုပ်မှုပမာဏကို ကြေညာခဲ့သည်။ ပိုမိုသိရှိလိုပါက, သွားရောက်ကြည့်ရှု ဝီကီပီးဒီးယား