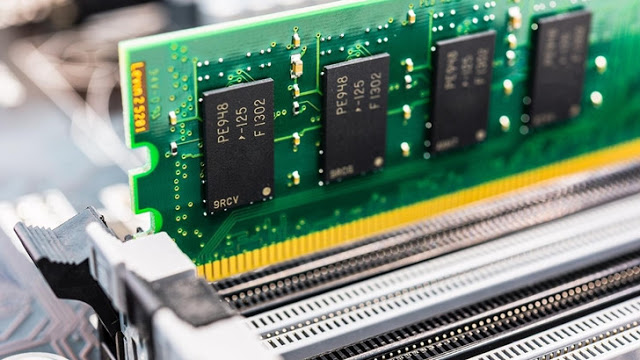

Umahluko phakathi kwe-DDR4 kunye ne-DDR5 RAM ikwisantya kunye namandla

Ngokombutho onoxanduva lwemigangatho yememori yekhompyuter eyaziwa ngokuba yi "JEDEC", isizukulwana esilandelayo se-DDR5 yememori yokufikelela ngokungahleliwe ("RAM") iya kukhawuleza kabini njenge-DDR4 RAM xa ikhutshwe.

I-JEDEC ibhengeze ukuba iyakugqibezela imigangatho ye-DDR5 ngaxesha lithile kwi-2018, kwaye umbutho uthi i-DDR5 iya kuphinda kabini i-bandwidth kunye noxinaniso ngaphezulu kwe-DDR4, kwaye iza kunye nokwanda kokusebenza kwamandla.

Nangona umgangatho uya kuba semthethweni kulo nyaka uzayo, isizukulwana esitsha asizukulungela abavelisi kude kube semva kowama-2020.

Kuyaphawuleka ukuba umgangatho weDDR4 wagqityezelwa ngo-2012, kodwa akuzange kube ngu-2015, xa iiprosesa kunye nee-SoCs kufuneka zihlaziywe ukuze zixhase.

Yintoni iDDR5

GDDR5 (Dual Graphics Data Rate v5) I-SDRAM luhlobo lwekhadi lemizobo ye-DRAM ephezulu yokusebenza eyenzelwe usetyenziso lwekhompyuter oluphezulu.

Njengomanduleli wayo, i-GDDR4, isekwe kwi-GDDR5 SDRAM DDR3 enemigca yedatha ephindwe kabini njenge-DDR2 SDRAM, kodwa ikwaqulathe i-GDDR5 ukusuka kwi-8-bit ebanzi ye-prefetch buffers efana ne-GDDR4. I-GDDR5 SGRAM ihambelana nemigangatho ekhankanywe kwinkcazo ye-GDDR5 yi-JEDEC. Isebenzisa i-DDR 8N ye-prefetch ye-architecture interface yokusebenza okuphezulu kunye nokusebenza okunokuthi kuqwalaselwe ukuba kuqhutywe kwi-32 x okanye i-16 x (i-clamshell) imowudi efunyenwe ngexesha lokuqaliswa kwesixhobo. I-GDDR5 2 i-interface yezothutho ine-32-bit yegama lekloko kumjikelo ngamnye (WCK) bhala idatha ukuya / ukusuka kwi-I / O izikhonkwane. Ufikelelo oluhambelanayo lubandakanya i -8N prefetch,

Okanye bhala okanye ufunde, ukusuka kumjikelo we-CK 2 wokudlulisa idatha kwi-256-bit clock ububanzi. Ingundoqo yememori yangaphakathi iqulethe i-32 ye-WCK yokudluliselwa kwedatha kwi-clock ehambelanayo ye-half-cycle clock kunye nobubanzi beebhithi ze-XNUMX kwiikhonkwane ze-I / O.

Umahluko phakathi kweDDR4 kunye neDDR5

I-GDDR5 isebenza ngohlobo olwahlukileyo lwewotshi. Umyalelo wokwahlukana kwewotshi (CK) njengereferensi yedilesi kunye namagalelo omyalelo, bhala umahluko wewotshi (WCK) njengereferensi efundayo nebhalayo. Ukuchaneka ngakumbi, ekujoliswe kuko kwiiwotshi ze-SGRAM GDDR5, nganye kuzo isetelwe kwii-byte ezimbini.

I-WCK isebenza ngokuphindaphindiweyo kwe-CK's frequency. Ukuthatha i-GDDR5 kunye ne-5 Gbit / s ireyithi yedatha ngephini nganye njengomzekelo, iwashi ye-CK isebenza kunye ne-1.25 GHz kunye ne-WCK kunye ne-2.5 GHz.

Iiwotshi ze-CK kunye ne-WCK ziya kulungelelaniswa ngexesha lokuqalisa kunye nokuqeqeshwa kokulandelelana. Oku kuhambelana kwenza ukuba ukufunda nokubhala kungabi naxesha lincinci. I-32-bit ye-GDDR5 enye kunye neePini, izicelo zethu ziye zabonisa kwaye zathatha isampula ye-GDDR5, kwaye yabonisa iphepha kubuchwepheshe obusemva kwe-GDDR5.

. NgoMeyi 10, 2008, uKimunda ubhengeze imiqulu yemveliso yeemodyuli ze-512 GDDR5 ezilinganiswe kwi-3.6 Gbit / s (900 MHz), 4.0 Gbit / s (1 GHz), kunye ne-4.5 Gbit / s (1.125 GHz). Ukuze ufumane inkcazelo engakumbi, tyelela Wikipedia